Редактор конечных автоматов

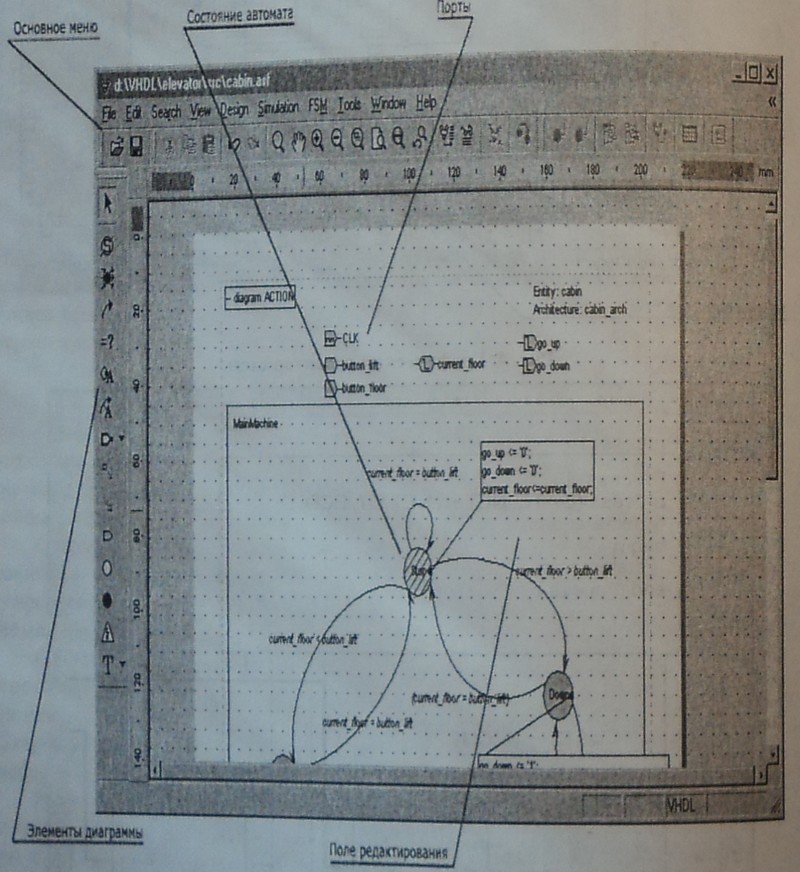

Редактор конечных автоматов (см. рис ниже) позволяет разрабатывать дискретные цифровые устройства в более наглядной, чем код на языке VHDL, нотации. Окно редактора конечных автоматов представлено на рисунке ниже и включает основное меню (инструментарий редактора), элементы диаграммы и поле редактирования. Результатом работы редактора является граф автомата, который затем однозначно интерпретируется в код на языке VHDL или Verilog.

Редактор конечных автоматов

Основными элементами графа автомата являются состояния (States) — вершины графа и переходы (Transitions) — направленные ребра графа. Кроме того, необходимо задать входные и выходные порты для автомата. На графе также могут отображаться другие элементы сущностей в УШЕЙЦ а именно: константы, сигналы, переменные и т.д.

В системе Active-HDL предусмотрена возможность создавать так называемые многоуровневые диаграммы, в основе которых лежат иерархические состояния (Hierarchical States). С их помощью можно разбить проект на функциональные блоки, описания которых будут отражены на отдельных графах.

Рассмотрим основные элементы графа автомата.

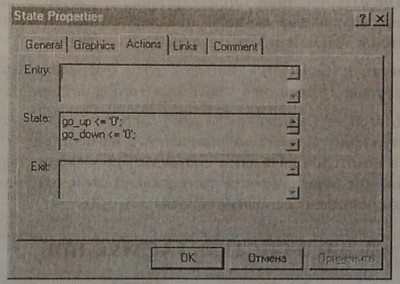

Состояние (State) — элемент графа, отображающий возможное состояние автомата. Различают обычные и иерархические состояния. Иерархическое состояние является графическим представлением вложенного функционального блока (внутреннего конечного автомата). Параметры состояний можно настроить в специальном диалоге (рис. ниже), где основной закладкой является Actions. В полях Entry, State и Exit необходимо задать действия, которые должны происходить в момент входа, «внутри» состояния и в момент выхода из состояния соответственно.

Настройка состояния

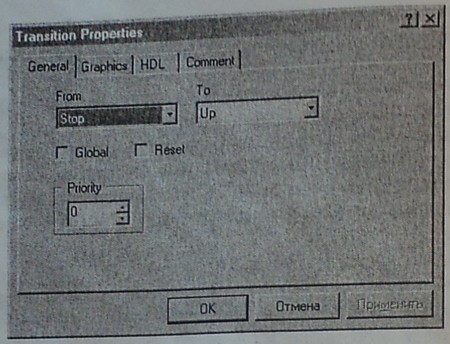

Переход (Transition) — элемент графа, отображающий возможный переход из одного состояния конечного автомата в другое при наступлении некоторых условий. Настройка перехода осуществляется в специальном диалоге рисунок ниже.

Настройка перехода

Порт (Port) — элемент графа, определяющий интерфейс взаимодействия проектируемого автомата с внешними по отношению к нему элементами проекта. Фактически порт является графическим представлением элемента port языка VHDL.

Сигнал/Переменная (Signal/Variable) — элемент графа, отражающий внутренние сигналы или переменных в соответствии с принятой в VHDL или Verilog нотации и семантике.

Константа (Constant) — элемент графа, отражающий константы в соответствии с принятой в VHDL или Verilog нотации и семантике.

Сброс (Reset) — элемент графа, обозначающий сброс схемы. В случае наступления события, обозначенного на переходе из состояния сброса в некоторое начальное состояние, происходит переход в это состояние вне зависимости от того, в каком состоянии находился автомат до наступления события сброса.