Разработка модели двоичного одноразрядного сумматора с переносом — Active-HDL

Пусть требуется разработать модель устройства «двоичный одноразрядный сумматор с переносом» на структурном уровне; структурное описание должно использовать библиотеку элементов, представляемых на поведенческом уровне. Описания схем компонентов будем представлять с использованием многозначной логики (библиотека std_logic).

Прежде всего, необходимо выбрать инструментарий для разработки. В данном случае модель удобнее разработать в виде текстового описания на языке VHDL, при этом описания отдельных элементов вынести в отдельную библиотеку.

Первоначально необходимо создать проект, который будет реализовывать модель сумматора — simple_adder. Для этого в меню File надо выбрать опцию New Design, затем в появившемся окне выбрать Create New design. В окне просмотра содержимого проекта выбрать пункт Add New File. В появившемся окне необходимо выбрать тип файла (VHDL) и задать его имя (gates.vhdl). В окне редактора необходимо ввести следующий код:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;package gates is

component and_2

generic (tpd_h1 : time := 1 ns;

tpd_lh : time :=1 ns);

port (in1, in2 : std_logic;

out1 : out std_logic);

end component;component or_2

generic (tpd_h1 : time := 1 ns;

tpd_lh : time := 1 ns);

port (in1, in2 : std_logic;

out1 : out std_logic);

end component;component xor_2

generic (tpd_hl : time := 1 ns;

tpd_lh : time := 1 ns);

port (in1, in2 : std_logic;

out1 : out std_logic);

end component;

end gates;library IEEE;

use IEEE.Std_Logic_1164.all;

—————————

— Элемент "И"

—————————

entity and_2 is

generic (tpd_hl : time := 1 ns;

tpd_lh : time := 1 ns);

port (in1, in2 : std_logic;

out1 : out std_logic);

end and_2;architecture only of and_2 is

begin

p1: process (in1, in2)

variable val : std_logic;

begin

val := in1 and in2;

case val is

when ‘0’ => out1 <= '0' after tpd_hl; when '1' => out1 <= '1' after tpd_lh; end case; end process; end only; -------------------------- -- Элемент "ИЛИ" -------------------------- library IEEE; use IEEE.Std_Logic_1163.all; entity or_2 is generic (tpd_hl : time := 1ns; tpd_lh : time := 1ns); port (in1, in2 : std_logic); out1 : out std_logic); end or_2; architecture only of or_2 is begin p1: process (in1, in2) variable val : std_logic; begin val := in1 or in2; case val is when '0' => out1 <= '0' after tpd_hl; when '1' => out1 <= '1' after tpd_lh; when others => out1 <= val; end case; end process; end only; -------------------------- -- Элемент "Исключающее ИЛИ" -------------------------- library IEEE; use IEEE.Std_Logic_1164.all; entity xor_2 is generic (tpd_hl : time := 1ns; tpd_lh : time := 1ns); port (in1, in2 : std_logic); out1 : out std_logic); end xor_2; architecture only of xor_2 is begin p1: process (in1, in2) variable val : std_logic; begin val := in1 xor in2; case val is when '0' => out1 <= '0' after tpd_hl; when '1' => out1 <= '1' after tpd_lh; when others => out1 <= val; end case; end process; end only;

В библиотеке определяются двухвходовые элементы И, ИЛИ, Исключающее ИЛИ, использующие многозначный алфавит

Перейдём к рассмотрению процесса описания моделируемого устройства. В окне просмотра содержимого проекта выберете пункт Add New File. В появившемся окне необходимо выбрать тип файла (VHDL) и задать его имя (adder.vhd). Теперь можно ввести структурное и поведенческое описания сумматора:

library IEEE;

use IEEE.Std_Logic_1164.all;entity simple_adder is

port (a : in std_logic;

b : in std_logic;

cin : in std_logic;

sum : out std_logic;

cout : out std_logic);

end simple_adder;— Описание простейшего сумматора при помощи

— параллельного присваивания (потоковая форма)architecture rtl of simple_adder is

begin

sum <= (a xor b) xor cin; cout <= (a and b) or (cin and a) or (cin and b); end rtl; -- Описание простейшего сумматора на -- структурном уровне -- Используем описания из библиоткеи gates use work.gates.all; architectrue structural of simple_adder is signal xor1_out, and1_out, and2_out, or1_out : std_logic; begin xor1: xor_2 port map (in1 => a, in2 => b, out1 => xor1_out);

xor2: xor_2 port map (in1 => xor1_out, in2 => cin, out1 => sum);

and1: and_2 port map (in1 => a, in2 => b, out1 => and1_out);

or1: or_2 port map (in1 => a, in2 => b, out1 => or1_out);

and2: and_2 port map (in1 => cin, in2 => or1_out, out1 => and2_out);

or2: or_2 port map (in1 => and1_out, in2 => and2_out, out1 => cout);

end structural;

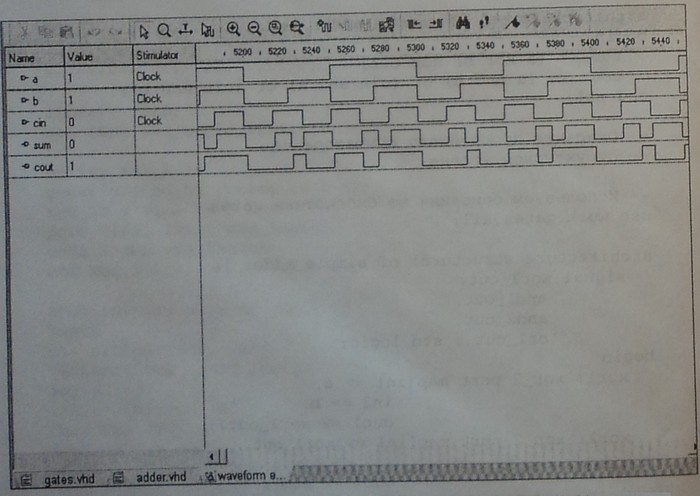

После компиляции полученного на предыдущих этапах разработки проекта появляется возможность построения временной диаграммы функционирования разработанной модели. Для построения временной диаграммы необходимо на вкладке проекта Structure выбрать целевое описание (simple_adder (structural) или simple_adder (rtl)), после чего в нижней половине окна добавить входные и выходные сигналы на временную диаграмму (в контекстном меню Add to Waveform). После генерации входных сигналов можно запустить модель на исполнение и получить результирующую диаграмму работы сумматора:

Диаграмма функционирования одноразрядного сумматора с переносом